文章信息

- 秦明伟, 高永翔, 李陈, 侯宝临, 王焕

- QIN Mingwei, GAO Yongxiang, LI Chen, HOU Baolin, WANG Huan

- 通用信道编译码算法物理性能快速仿真系统

- Fast simulation system for physical performance of universal channel codecs

- 中国测试, 2024, 50(6): 98-105

- CHINA MEASUREMENT & TEST, 2024, 50(6): 98-105

- http://dx.doi.org/10.11857/j.issn.1674-5124.2022070150

-

文章历史

- 收稿日期: 2022-07-26

- 收到修改稿日期: 2022-09-15

随着未来网络的大规模部署和无线信道的日益拥挤,无线信道电磁环境愈发复杂,信道编码技术在对抗干扰、提升通信可靠性方面的作用更为凸显[1]。对于不同的无线信道环境,需要设计不同的信道编码方法及参数,以实现通信性能最优[2]。仿真作为通信技术领域的一种重要研究手段,是评估通信系统性能设计的重要途径[3]。在进行信道编码方式选择与参数设计时,采用仿真技术能够实现不同编译码算法选择及参数设计下的通信系统性能快速评估验证,为工程设计中的系统参数分配提供决策依据。

尚启星和鲁芳旭等[4-5]在针对Reed-solomon(RS)码开展的编译码算法性能研究中,分别基于Matlab工具搭建仿真系统模型进行性能验证与分析工作;詹平红和曲国伟等[6-7]在针对Low-density Parity-check(LDPC)码开展的编译码算法性能研究中,也采用了将算法数学模型转换为计算机仿真模型(如Matlab)的方法进行性能验证。这种使用计算机仿真软件,对信道编译码算法建立仿真模型开展性能验证的方法,能够提升系统设计效率,但软件程序为解释执行的方式,仿真工具受计算机性能影响,存在仿真速度慢、效率低,且受限于计算机性能无法应对大数据量仿真分析的需求场景等问题。吴博[8]在针对LDPC并行译码算法开展研究时,为了提升仿真效率,采用基于Graphics Processing Unit(GPU)硬件加速的方法来构建仿真系统,运算效率相较传统计算机仿真方法提升了17倍。该方法通过提升仿真软件依托的计算机平台运算性能来加速运算,其本质仍然是计算机软件仿真,其基于浮点数或定点数的仿真模型脱离了算法的物理实现架构,与实际应用场景中算法逻辑硬件化后的物理模型有着较大差异,导致性能评估结果与工程实际有着较大差距,不能准确地指导工程实际的参数设计,且该种方法仿真效率仍然较低,运算速度明显受仿真平台性能影响极大。

为了获得信道编译码算法实际物理硬件逻辑实现的准确性能,即使在已有编译码算法硬件代码的前提下,研究人员仍然需要基于工程设计需求,独立搭建完整的硬件算法验证系统。夏阁淞等[9]在针对极化码存在译码延迟大、吞吐量低、硬件消耗量大等问题展开研究时,为了准确验证算法性能,基于Field Programmable Gate Array(FPGA)芯片完成了译码算法的硬件逻辑设计,并构建了硬件验证系统;刘梦欣[10]在基于FPGA的RS编译码研究工作中,部分考虑的验证系统的通用性,能够支持不同长度和码率的RS码译码算法硬件逻辑实现性能的验证;Takashi等[11]基于FPGA开展了RS+LDPC级联码编译码算法硬件逻辑实现的性能验证系统构建与性能评估工作;宿凌超等[12]针对DVB-S标准中RS+CC级联码编译码算法硬件逻辑实现的性能验证需求,设计了半实物仿真系统,能够支持不同删余参数下QPSK调制的性能验证。这种基于电路的信道编译码算法性能仿真评估方法,能够准确反映信道编译码算法的实际物理性能、置信度更高,能够更加准确地指导工程开发与参数设计。然而,受限于硬件算法设计开发周期长、移植难度大、对仿真评估人员技术门槛要求较高等因素,该类方法多为工程设计人员针对具体需求进行评估所用,多数也只能对应一种应用场景,推广性和通用性都存在较大缺陷。

针对上述问题,邓莉[13]基于RS+CC级联码设计了信道编解码算法性能快速验证系统。系统支持两种码型在不同码率、不同编码方式以及不同调制模式下抗噪声性能的快速评估,距离具有良好通用性和可移植性,能够支持不同信道编译码算法、信道加噪方式、调制解调模式,并具有良好人机交互性,与具备仿真数据统计分析能力的通用信道编译码算法物理性能快速仿真系统相比仍有较大差距。基于上述研究的不足和当前工程设计领域对信道编译码算法物理硬件实现性能快速评估的需求,采用PC上位机软件与FPGA下位机硬件相结合的软硬件协同仿真系统架构,提出了一种通用信道编译码算法硬件实现物理性能快速仿真评估系统的实现方法。

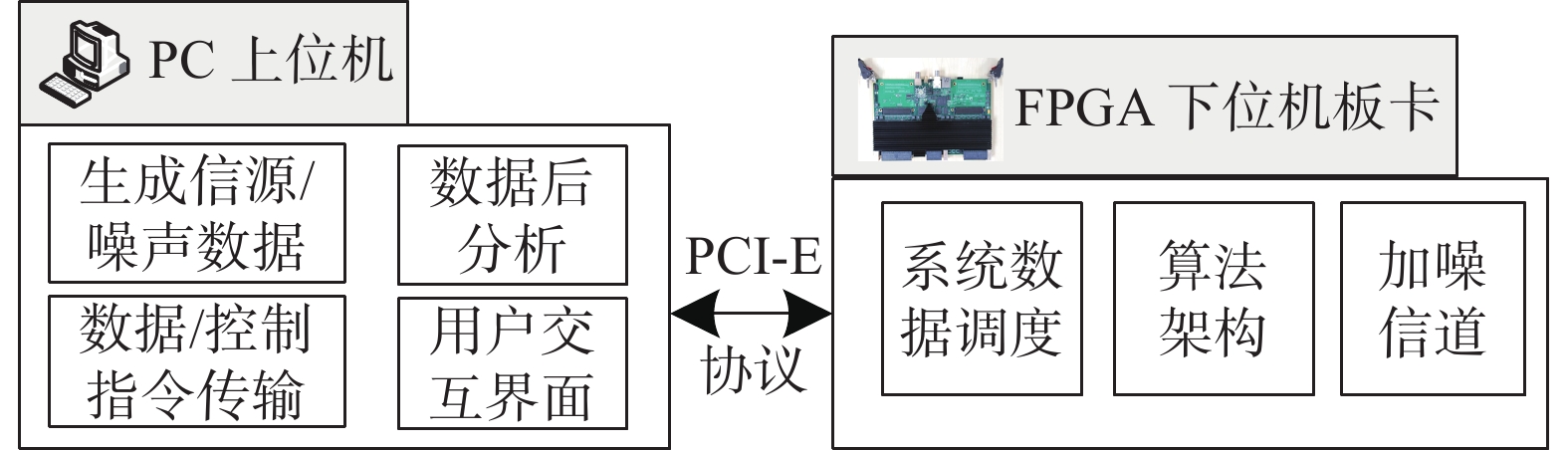

1 系统仿真模型设计 1.1 系统设计目标系统设计目标是建立一个具备通用性的信道编译码算法性能仿真与评估系统,系统功能任务分解如图1所示。PC上位机软件主要实现模拟信源/噪声数据的生成、仿真数据的后分析、数据/控制指令传输和与FPGA的用户交互界面4部分功能;FPGA下位机实现为算法仿真提供仿真源数据和仿真过程的数据调度功能、信道编译码算法仿真和信道噪声叠加的功能;PC上位机和FPGA通过PCI-E总线完成数据交互。

|

| 图 1 系统功能图 |

1.2 系统仿真模型结构

系统任务结构与映射如图2所示。在FPGA下位机硬件上部署仿真系统的数据调度与控制、编码与调制和加噪信道3个逻辑功能单元。系统数据调度单元提了大容量缓冲空间,其中,DDRA存储器用于接收上位机下发的各类原始仿真源数据,DDRB存储器用于采集用户指定的仿真过程数据,并实时回传至上位机。通过设计通用化标准FIFO接口与数据读写机制,保证了数据缓冲调度单元对各种信道编译码算法的兼容性,以及仿真过程的实时性、高效性、通信数据的连续性。算法验证单元提供了标准的外码+交织+内码信道编译码算法架构和通用的误码性能统计功能,该单元以主动模式从缓冲区读取数据,以流处理方式驱动信道编码、交织、调制、加噪、解调、解交织以及译码等模块工作,从而实现算法性能仿真,并根据系统控制指令,采集用户指定的仿真过程数据写入缓冲调度单元,并进行误码率等特性参数计算,从而实现各种编译码算法性能的真实、有效评估。加噪信道在算法验证单元数据流的驱动下工作,可支持两种加噪方式,分别为上位机事先生成噪声的加入以及根据用户设定参数由下位机模拟信道实时生成噪声加入。系统整体受系统控制模块主控,主控信息由PC端通过寄存器通道下传至系统控制模块进行解析执行。

|

| 图 2 系统实现架构 |

算法仿真部分电路模块结构设计如图3所示。模块中当前部署了部分常用的通信标准中的信道编译码算法,如RS码、BCH码、卷积交织、删余卷积码和LDPC码等信道编译码算法模块,各算法模块可根据cmd参数配置信息实现不同方式的级联。系统当前支持QPSK调制解调方式,用户可根据需要灵活扩展;各算法模块接口均设计为AXI标准接口,并且以IP化的方式添加到电路设计中;系统预留开放式I/O口,在使用过程中,用户可以根据需求在系统框架中集成更多的信道编译码算法。数据管理模块控制仿真源数据管理和仿真过程数据管理,仿真源数据管理模块用于从系统数据调度模块主动读取所需的信源数据以及信道加噪所需的噪声,信源数据接入外码模块,噪声数据接入信道模块;仿真过程管理模块管理仿真过程中各模块输出数据,便于数据的上传处理以及误码统计。功能管理模块实现编译码系统控制参数配置和误码率统计功能。编译码系统控制参数配置模块用于给各算法模块提供仿真参数,如系统仿真编码方式、码率、调制方式、系统复位和使能控制;误码率统计通过仿真过程数据管理模块接入外码、交织、内码、信道数据,通过对比,计算出各级的误码数,待仿真完成后,上传至上位机软件计算误码率并分析性能。

|

| 图 3 算法仿真电路模块结构 |

2 加性高斯白噪声仿真信道设计

加噪信道是系统的一个重要组成部分。信道中的噪声由众多原因导致,但依据中心极限定理可知,大量的小随机变量的积累效应近似于正态分布。通常情况下,会使用加性高斯信道模型来表征此类通信信道模型。高斯信道是恒参信道,如光纤通信、卫星通信、同轴电缆通信等均可视为高斯信道,所以对加性高斯信道(AWGN)的研究有重要现实意义。因此,系统当前集成了这一常用的信道模型,后续可根据实际需求灵活扩展,如瑞利信道、莱斯信道等,并可考虑引入多径等影响因素。

加性高斯白噪声的功率谱密度在整个信道带宽上恒定为

| $ \begin{split} & P{\text{(}}{O_1} = {o_1},{O_2} = {o_2}, \cdots ,{O_{{n}}} = {o_{{n}}}|\\ & {I_1} = {i_1},{I_2} = {i_2}, \cdots ,{I_{{n}}} = {i_{{n}}}{\text{)}} = \prod\limits_{k = 1}^n {P({O_{{k}}} = {o_{{k}}}|{I_{{k}}} = {i_{{k}}})} \end{split} $ | (1) |

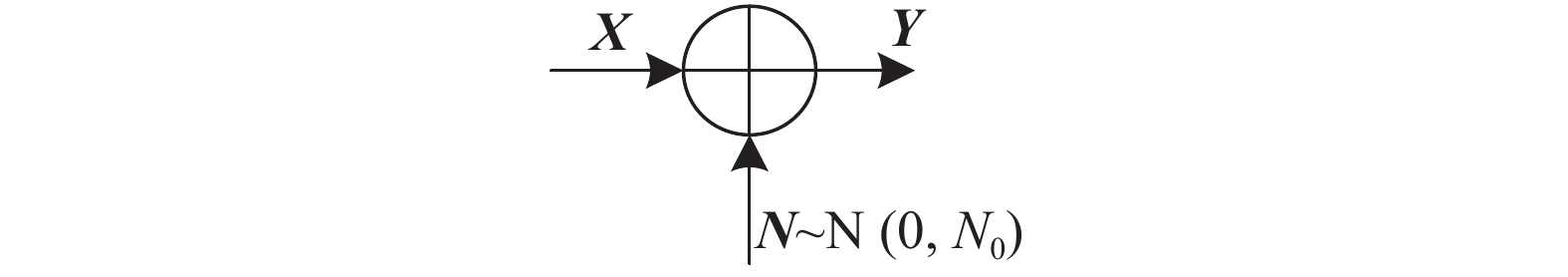

离散无记忆信道模型如图4所示,虽然输入信号时离散序列,但高斯信道中的噪声确是满足高斯分布的连续噪声信号,因而输出信号也是连续变量。从一组包含

|

| 图 4 离散无记忆高斯信道模型 |

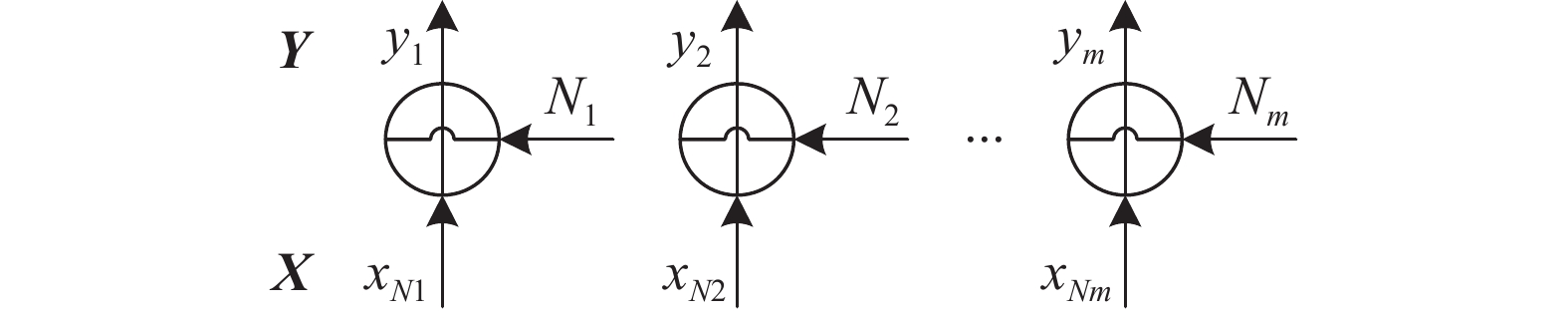

若把信道的输入

|

| 图 5 矢量离散无记忆高斯信道模型 |

输入信号功率为:

| $ {P_{\text{S}}} = \frac{1}{n}\sum\limits_{i = 1}^n {{x_{{i}}}} $ | (2) |

根据信噪比计算公式:

| $ {\mathrm{SNR}} = 10{\text{l}}{{\text{g}}}\frac{{{P_{\mathrm{S}}}}}{{{P_{\mathrm{N}}}}} $ | (3) |

可求得噪声功率

用于描述AWGN信道中噪声相对功率的典型量包括:

| $ {E_{\text{s}}}/{N_{\text{0}}}{\text{(dB)}} = {E_{\text{b}}}/{N_0}{\text{(dB)}} + 10 \times {\text{l}}{{\text{g}}}{\text{}}k{\text{}} $ | (4) |

其中

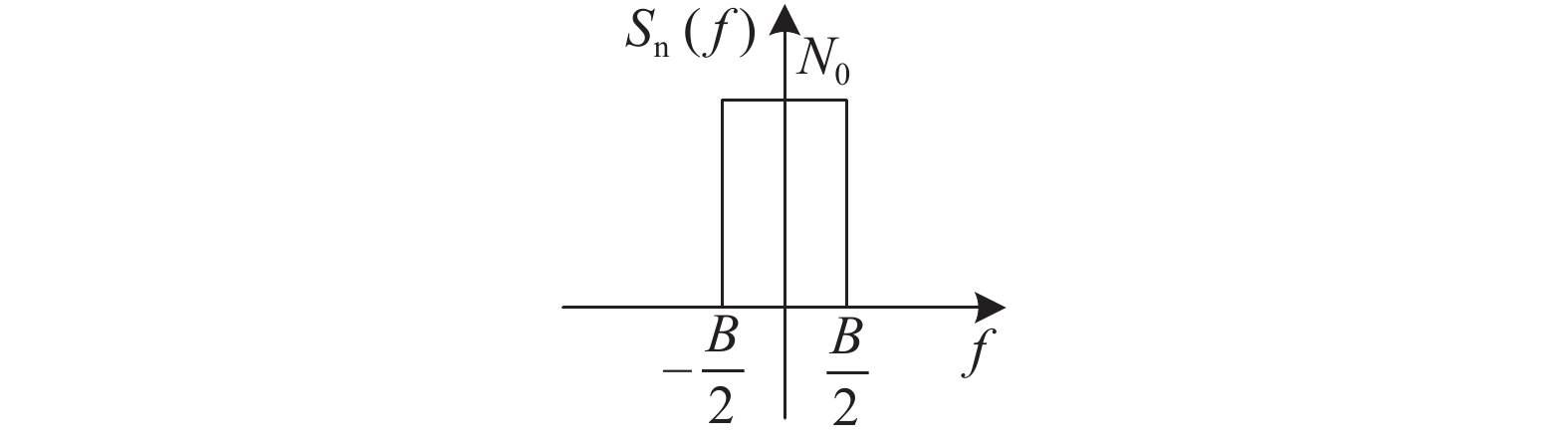

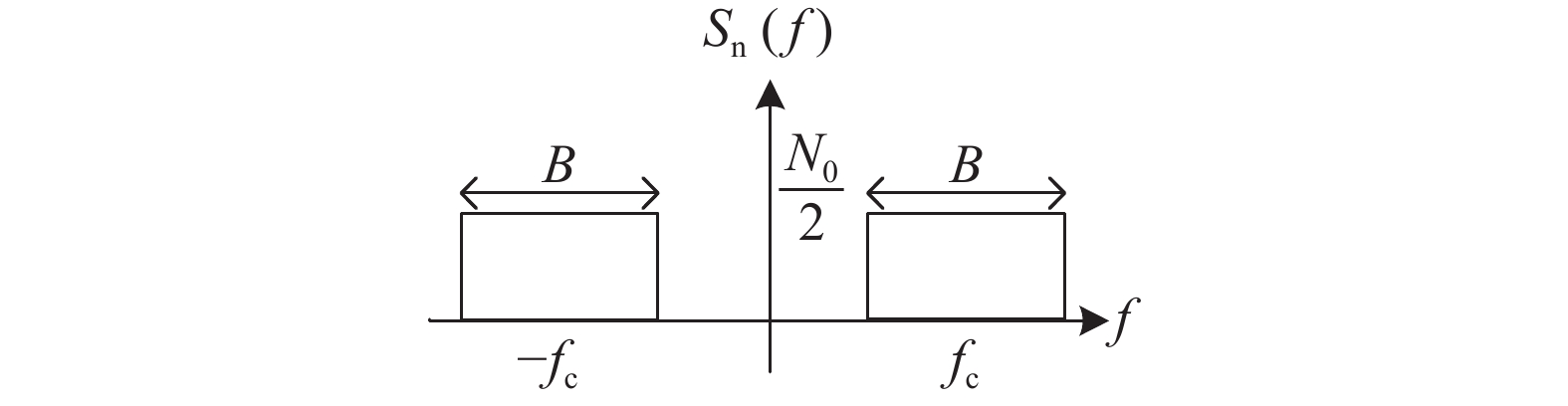

输入为复信号时,噪声功率谱如图6所示,因此,

|

| 图 6 输入复信号噪声功率谱密度 |

| $ \begin{split} {E_{\text{s}}}/{N_0}{\text{(dB)}} = \;&10{\text{l}}{{\text{g}}}{\text{((}}S \cdot {T_{{\text{sym}}}}{\text{)}}/{\text{(}}N/{B_{\text{n}}}{\text{))}} = \\ \;& 10{\text{l}}{{\text{g}}}{\text{((}}{T_{{\text{sym}}}} \cdot {F_{\text{s}}}{\text{)}}/{\text{(}}S/N{\text{))}} = \\ \;&10{\text{l}}{{\text{g}}}{\text{(}}{T_{{\text{sym}}}}/{T_{{\text{sample}}}}{\text{)}} + {\mathrm{SNR}} \end{split}$ | (5) |

式中:Tsym——信号的符号周期;

Tsample——信号的采样周期;

输入为实信号时,噪声功率谱如图7所示。因此

|

| 图 7 输入实信号噪声功率谱密度 |

| $ {E_{\text{s}}}/{N_0} = 10{\text{l}}{{\text{g}}}{\text{(}}0.5{T_{{\text{sym}}}}/{T_{{\text{sample}}}}{\text{)}} + {\rm{SNR}} $ | (6) |

在该系统中由PC机使用Matlab生成0,1二值化的信息数据,信息数据经映射后,符号功率固定,根据式(3)在已知信号功率与信噪比值可求得噪声功率,由此可得噪声量化范围。以QPSK调制模式、符号功率为16个单位功率为例,考虑硬件实现后的截断误差,理论噪声功率、实际产生的噪声功率、量化位宽(包含符号位)、量化后噪声功率,量化后实际信噪比计算如表1所示。由表可知,当符号功率为16个单位功率、调制方式为QPSK时,需要的噪声信号最大位宽为7 bit,由于实验次数有限,考虑系统设计冗余,最终选取噪声量化位宽为8 bit。

| 理论信噪比/dB | 理论计算噪声功率 | 实际产生噪声功率 | 量化后噪声功率 | 噪声位宽(带符号位)/bit | 实际信噪比/dB |

| –7 | 160.3799148 | 157.6426195 | 157.886 | 7 | –6.931936438 |

| –6 | 127.3942946 | 124.8097269 | 124.9525 | 7 | –5.915949714 |

| –5 | 101.1928851 | 101.0807357 | 101.2077 | 7 | –5.000635771 |

| –4 | 80.38036581 | 78.17323613 | 78.2781 | 7 | –3.884902974 |

| –3 | 63.84839408 | 65.36400561 | 65.4557 | 6 | –3.107974934 |

| –2 | 50.71658216 | 51.12265556 | 51.1862 | 6 | –2.040029109 |

| –1 | 40.28561318 | 40.14535006 | 40.2592 | 6 | –0.997151624 |

| 0 | 32 | 30.96728621 | 31.0709 | 6 | 0.127961451 |

| 1 | 25.41850351 | 25.20450929 | 25.313 | 6 | 1.018063592 |

| 2 | 20.19063502 | 20.50781053 | 20.5897 | 6 | 1.914999595 |

| 3 | 16.03799148 | 16.34984252 | 16.4329 | 6 | 2.894357659 |

| 4 | 12.73942946 | 12.77009621 | 12.8823 | 5 | 3.951565696 |

| 5 | 10.11928851 | 10.45067632 | 10.5314 | 5 | 4.8266387 |

| 6 | 8.038036581 | 8.019310263 | 8.0892 | 5 | 5.972444051 |

| 7 | 6.384839408 | 6.346643135 | 6.4348 | 5 | 6.966149252 |

| 8 | 5.071658216 | 5.06792997 | 5.1481 | 5 | 7.93503004 |

| 9 | 4.028561318 | 3.941869779 | 4.0372 | 5 | 8.990697137 |

| 10 | 3.2 | 3.237417163 | 3.3163 | 4 | 9.844961674 |

3 系统软硬件平台实现 3.1 上位机软件

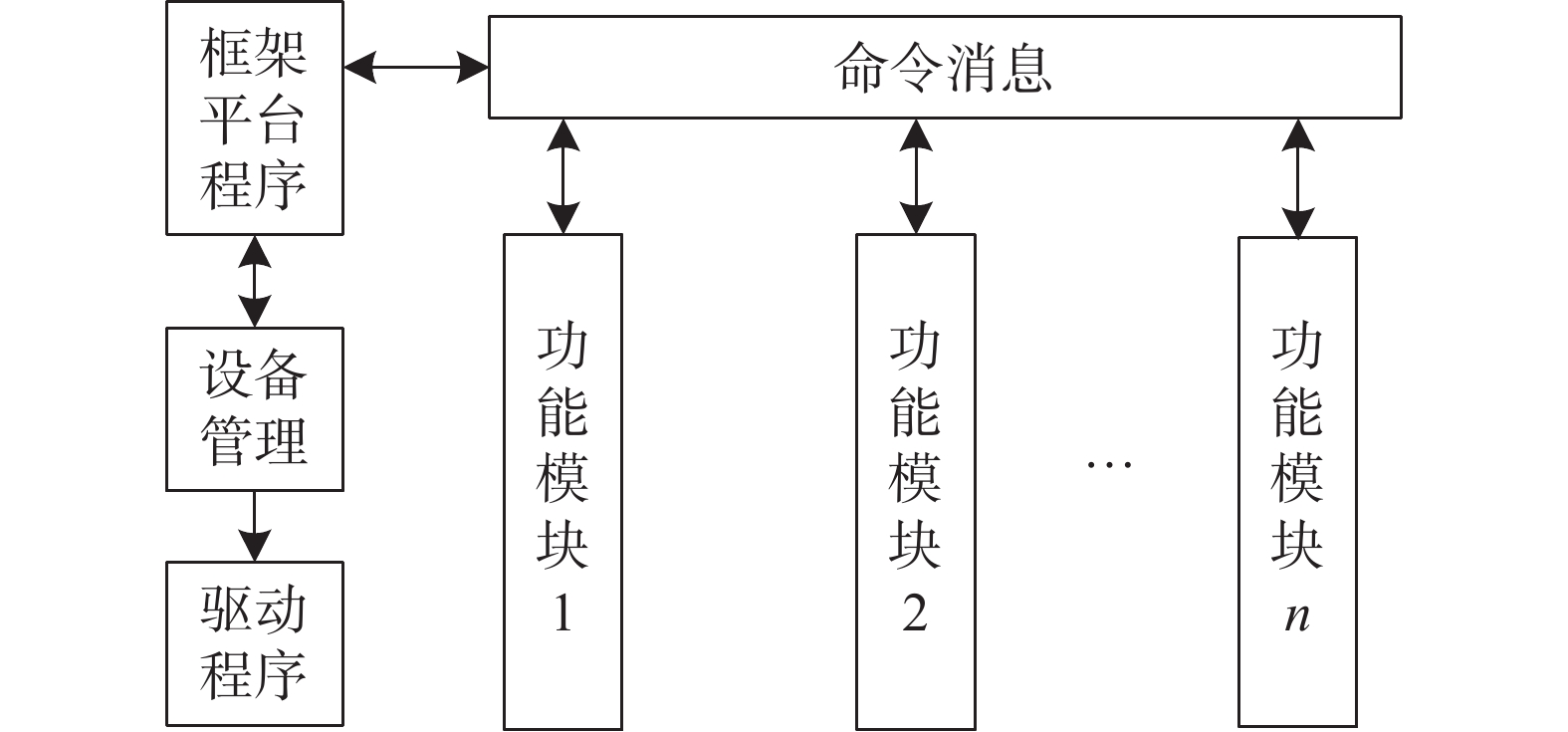

软件平台开发环境使用Visual Studio,开发语言使用C#。以动态链接库为基础,采用标准通信协议以及对相关接口进行规范,如此形成的上位机环境,可重构且是开放性的。上位机软件作为系统的主控,控制硬件系统的工作,根据模块化原则,软件系统结构如图8所示。其主要由框架平台程序、设备管理、设备驱动程序、功能模块等模块组成。其中,框架平台程序提供命令管理机制,功能模块及其与设备管理间的交互、设备的启动/关闭。设备管理主要是在系统启动时初始化硬件设备、控制设备工作、加载参数供上层程序调度等。驱动程序包括设备驱动程序和驱动程序API动态库[10]。这种体系结构方便了独立新功能模块的开发。

|

| 图 8 软件体系结构框图 |

3.2 系统实物平台

硬件平台使用搭载Xilinx Virtex7 690T FPGA的信号处理卡,拥有丰富的逻辑和布线资源,便于实现多种仿真算法的硬件部署;FPGA信号处理卡上搭载两片2 GB容量的DDR3存储颗粒,可实现仿真源数据和仿真过程数据的大容量缓存,基于大容量的数据缓存作为完成数据调度,使系统可以支持在计算机仿真上无法实现的大数据量的仿真分析。系统测试验证实物平台如图9所示,左侧为VPX总线架构的机箱,机箱内部构成有FPGA信号处理卡和计算机主板。系统的仿真验证的硬件实现通过FPGA信号处理卡完成。右侧是上位机软件界面,上位机软件在计算机主板上运行,二者通过高速总线互连接,实现FPGA与PC之间的高速通信,控制指令和仿真数据下传以及仿真过程数据和系统误码率统计的回传分析。

|

| 图 9 系统测试验证实物平台 |

4 系统性能分析

对整个系统进行性能测试,在上位机生成不同信噪比的噪声数据下传至FPGA,分别测试了RS编/译码,卷积交织/解交织,卷积编码/维特比译码,级联码(RS码+卷积交织+卷积码)在–7~9 dB等16种信噪比环境下算法的物理性能。

以级联码(RS码+卷积码)为例,选择QPSK调制方式,采用经过工程应用验证的编译码算法硬件逻辑实现代码,在上位机软件用户交互界面配置好仿真参数后,系统自动完成了配置的16种信噪比环境下的编译码结果仿真分析,仿真过程数据正确上传,软件正确绘制内码和外码的性能分析曲线。测试结果表明,系统能按照配置参数完成编码、调制、加噪、解调、译码、数据传输和误比特性能统计等功能,且系统支持批处理模式,可实现多模式多种仿真参数的自动化仿真。

信道译码算法在硬件化实现过程中,FPGA在浮点数的计算时,只能将浮点数转换为定点数进行运算,得到的计算结果会有精度损失,使硬件化后的算法会有一定的性能恶化。系统完成仿真实验后,通过调用预先编写的Matlab函数,使用相同的信源和噪声数据模拟算法相同的仿真过程,对比分析二者仿真结果,验证系统的可靠性。以删余卷积码和RS码、QPSK调制方式为例,在Matlab上使用相同信源数据和噪声数据进行相同过程的仿真分析,然后将Matlab软件仿真结果与信道编解码算法性能半物理仿真系统硬件实测结果进行比对(图10)。对比仿真分析得出,删余卷积码1/2、2/3、3/4、5/6以及7/8五种删余模式和RS码仿真结果的误码率始终处于同一个数量级,算法硬件化后仿真结果与软件结果基本一致。性能恶化最大值未超过0.4 dB,处于该编译码算法硬件逻辑实现后的性能误差范围中,较小的性能恶化说明所设计系统的可靠性,可以较为准确地仿真验证出信道编译码算法的物理性能。

|

| 图 10 删余卷积码及RS码软硬件性能对比 |

对系统的仿真效率测试,验证卷积码(2,1,7),维特比译码算法性能时,测试仿真源数据比特量为10的7次方量级,进行一次或多次实验,上传一种或多种类型的数据等方式进行测试,系统执行仿真耗时统计结果如表2所示,与采用Matlab进行仿真单次实验时长达数分钟甚至小时相比,本系统在仿真耗时上占有明显优势,仿真效率更高。

| 序号 | 测试模式 | 仿真耗时/s |

| 1 | 单次实验/1种数据 | 11.10 |

| 2 | 单次实验/1种数据 | 9.46 |

| 3 | 单次实验/4种数据 | 26.72 |

| 4 | 单次实验/4种数据 | 26.60 |

| 5 | 多次(17)实验/1种数据 | 140.70 |

| 6 | 多次(17)实验/1种数据 | 140.25 |

| 7 | 多次(17)实验/4种数据 | 434.15 |

| 8 | 多次(17)实验/4种数据 | 435.12 |

5 结束语

本文采用PC上位机软件与FPGA下位机结合的软硬件协同设计架构,提出了一种通用化的信道编译码算法仿真系统实现方法。论述了原型系统的总体开发框架,基于VPX机箱构建了实物系统,并以RS码、卷积码等码型完成了闭环性能测试。测试结果表明,系仿真统编码方式、调制方式、信道类型与信噪比参数切换灵活,支持批处理仿真功能,能快速得到大数据量下多模式信道编译码算法的物理性能分析结果,仿真效率高、仿真结果真实可靠,能够为工程设计提供准确的设计参考。系统提供开放式I/O口,系统可移植性强,为系统后续算法应用场景的变换扩充提供了有效的解决方案。

| [1] |

陈曦原. 信道编码技术在卫星通信中的重要应用研究[J].

数字通信世界, 2019, 2(2): 172-175.

|

| [2] |

路文娟, 张辉, 张世强. 无线传感器网络节点通信与定位综合信号设计[J/OL]. 中国测试: 1-6[2022-09-16]. http://kns.cnki.net/kcms/detail/51.1714.TB.20211202.1752.004.html.

LU W J, ZHANG H, ZHANG S Q. Integrated signal design for communication and positioning of wireless sensor network nodes[J/OL]. China Measurement & Test: 1-6[2022-09-16]. http://kns.cnki.net/kcms/detail/51.1714.TB.20211202.1752.004.html.

|

| [3] |

富璇, 杨毅, 何思远, 等. 基于Matlab的现代通信系统的仿真应用[J].

沈阳工程学院学报(自然科学版), 2007(4): 367-370.

|

| [4] |

尚启星. RS码在通信中的性能分析与仿真[J].

软件导刊, 2014, 13(11): 37-38.

|

| [5] |

鲁芳旭, 刘翠海. RS码的性能分析与仿真[J].

数字技术与应用, 2020, 38(8): 25-27.

|

| [6] |

詹平红, 李红星, 尹爱兵. LDPC编译码算法的仿真分析[J].

计算机与数字工程, 2019, 47(5): 5.

|

| [7] |

曲国伟, 宋晓萍. 低密度奇偶校验码的混合译码算法[J].

系统仿真学报, 2018, 30(10): 4009-4013.

|

| [8] |

吴博. 基于DVB-S2标准的LDPC并行译码算法研究与GPU实现[D]. 成都: 西南交通大学, 2019.

WU B. Research on LDPC parallel decoding algorithm based on DVB-S2 standard and GPU implementation[D]. Chengdu: Southwest Jiaotong University, 2019.

|

| [9] |

夏阁淞, 葛万成. 极化码译码算法的改进与FPGA实现[J].

通信技术, 2019, 52(11): 2611-2616.

|

| [10] |

刘梦欣. 基于FPGA的RS编译码研究与设计[D]. 太原: 中北大学, 2020.

LIU M X. Research and design of RS codec based on FPGA[D]. Taiyuan: North University of China, 2020.

|

| [11] |

MIZUOCHI T, KONISHI Y, MIYATA Y, et al. Experimental demonstration of concatenated ldpc and rs codes by fpgas emulation[J].

IEEE Photonics Technology Letters, 2009, 21(18): 1302-1304.

DOI:10.1109/LPT.2009.2025867 |

| [12] |

宿凌超, 雷茂, 秦明伟, 等. 基于半实物仿真的信道编译码性能验证系统[J].

制造业自动化, 2022, 44(4): 62-65.

|

| [13] |

邓莉. 信道编解码算法性能快速验证系统设计[D]. 绵阳: 西南科技大学, 2020.

DENG L. Design of system for rapid verification of channel codec algorithm performance[D]. Mianyang: Southwest University of Science and Technology, 2020.

|

2024, Vol. 50

2024, Vol. 50